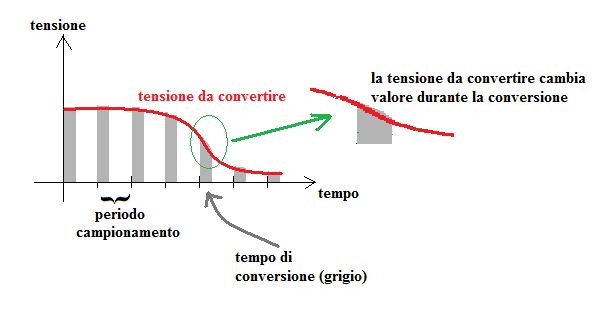

Per eseguire correttamente una conversione analogico-digitale, la tensione all’ingresso del convertitore ADC non dovrebbe cambiare valore durante il tempo di conversione (Tconversione) dell'ADC. In caso contrario infatti la conversione risulterebbe errata, poiché il valore da convertire non sarebbe definito con precisione.

E' evidente che il problema si verifica quando il segnale da convertire cambia con una velocità maggiore del tempo impiegato dal convertitore per convertirlo.

Una situazione analoga si verifica in fotografia quando il tempo di apertura dell'otturatore della macchina fotografica è troppo lungo e il soggetto è in movimento veloce. Il risultato che si ottiene è una fotografia "mossa".

Sarebbe possibile dimostrare che la conversione avviene senza errore apprezzabile (o meglio, senza introdurre un errore maggiore a quello di quantizzazione) a condizione che sia:

fmax ≤ 1/(π * 2n * Tconversione)

dove

- fmax è la massima frequenza del segnale da convertire

- n è la risoluzione (numero di bit) del convertitore

- Tconversione è il tempo di conversione del convertitore

- π è la costante pi greco (3.1415)

Si noti che fmax si riduce:

- all'aumentare di Tconversione: ciò corrisponde a usare un convertitore lento e dunque non in grado di "fotografare" segnali che variano troppo rapidamente;

- all'aumentare del numero di bit n del convertitore: se aumenta n, aumenta anche la precisione della conversione e dunque anche piccole variazioni del segnale di ingresso durante la conversione verrebbero rilevate dall'ADC; se il convertitore è molto preciso, il segnale dev'essere lento per poter essere "misurato" con la precisione richiesta durante il tempo di conversione.

Facciamo un esempio pratico. Supponendo di usare un converitore a 8 bit con Tconversione = 1 µs abbiamo

1/(π * 2n * Tconversione) = 1/(3.14 * 256 * 10-6) = 1244 Hz

Pertanto il nostro ADC è in grado di convertire correttamente solo segnali con frequenza massima inferiore a 1244 Hz circa. Si osservi che con Tconversione = 1 µs in teoria sarebbe possibile usare una fcampionamento di 1 MHz e dunque convertire, in base al teorema del campionamento, segnali con banda fino a 500 kHz. Dunque la limitazione su fmax dovuta al tempo di conversione non nullo dell'ADC è generalmente molto più stringente di quella dovuta al teorema del campionamento.

Quando il convertitore è troppo lento rispetto alla variazione del segnale da convertire, ovvero quando la diseguaglianza

fmax ≤ 1/(π * 2n * Tconversione)

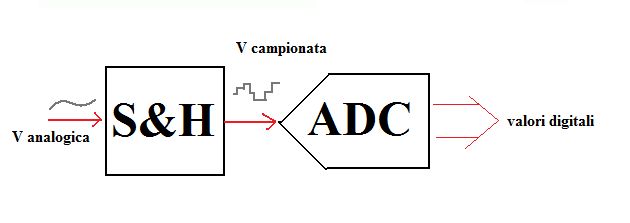

non è verificata, si utilizza un circuito, posto a monte del convertitore ADC, con lo scopo di mantenere costante la tensione da convertire per tutta la durata della conversione stessa. Tale circuito si chiama Sample and Hold (abbreviato S&H) ovvero in italiano campionamento e mantenimento.

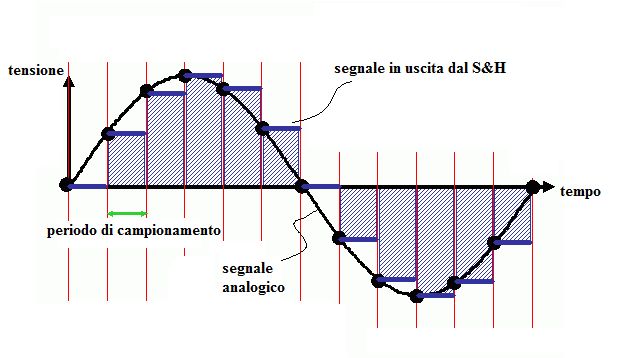

In pratica il S&H "congela" la tensione da convertire per tutta la durata del periodo di campionamento, in modo tale che l'ADC abbia il tempo di effettuare una conversione corretta.

Ovviamente la frequenza di campionamento del S&H coincide con la frequenza di campionamento dell'ADC.

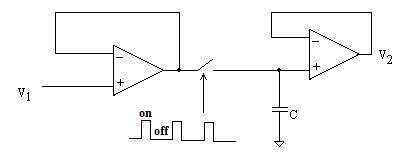

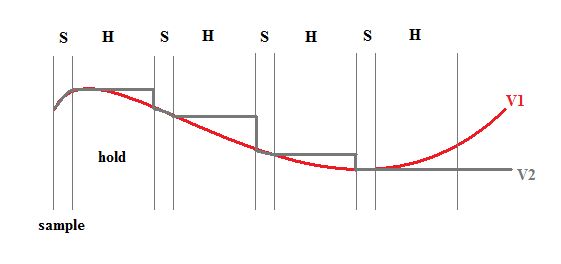

Dal punto di vista logico, il S&H è realizzato mediante un interruttore elettronico comandato da una tensione digitale di controllo:

Nella figura precedente V1 è la tensione analogica da campionare e V2 è la tensione analogica campionata; il treno di impulsi digitali comanda la chiusura dell'interruttore a ogni periodo di campionamento: on indica la chiusura dell'interruttore e off la sua apertura (idealmente ton deve sempre essere molto minore di toff e ton+toff=Tcampionamento); il condensatore (detto hold capacitor) serve per mantenere costante la tensione quando l'interruttore viene aperto; i due buffer servono per isolare il condensatore dai circuiti posti a monte e a valle del S&H.

Durante la fase di sample l'interruttore viene chiuso (on) e il condensatore si carica a un valore di tensione uguale a V1; durante la fase di hold l'interruttore è aperto (off) e il condensatore mantiene una tensione costante che, attraverso il secondo buffer, viene riportata sull'uscita V2.

La durata della fase di sample dev'essere idealmente la più breve possibile ed è determinata dal tempo di apertura (aperture time) dell'interruttore elettronico, cioè dal tempo che l'interruttore impiega per aprirsi. Infatti durante tale tempo il segnale in uscita V2 non è stabile, ma segue l'andamento della tensione di ingresso V1.

Il tempo di apertura del S&H limita la massima frequenza di segnale fmax che può essere convertito, secondo la stessa formula che abbiamo visto prima (dove ora al posto di Tcampionamento abbiamo Tapertura):

fmax ≤ 1/(π * 2n * Tapertura)

I circuiti di sample and hold commerciali possono comunemente avere tempi di apertura inferiori al nanosecondo.

Considerando di nuovo l'esempio precedente, quello cioè di un convertitore a 8 bit e tempo di conversione di 1 µs, abbiamo visto come tale convertitore sia in teoria in grado di campionare segnali con una banda massima di 500 kHz (alla frequenza di Nyquist). Tuttavia tale frequenza non può essere raggiunta a causa delle variazioni del segnale di ingresso durante il tempo di conversione. Per raggiungere la massima frequenza di campionamento teoricamente ottenibile con tale ADC, occore anteporre al convertitore un blocco di S&H con tempo di apertura che può essere così ricavato:

fmax ≤ 1/(π * 2n * Tapertura) →Tapertura≤ 1/(π * 2n * fmax) = 1/(3.14 * 256 * 500k) = 2,5 ns

Sito realizzato in base al template offerto da

http://www.graphixmania.it