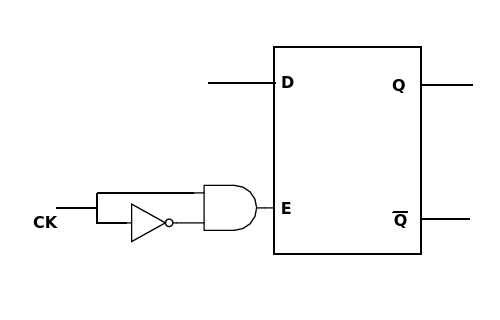

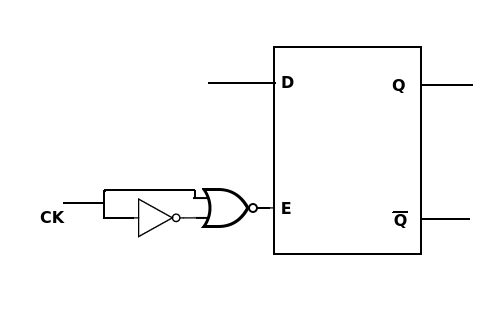

Consideriamo il seguente circuito ottenuto modificando un latch D:

A causa della presenza della porta NOT sembrerebbe che l'ingresso E del latch non possa mai essere abilitato (livello H): infatti i due ingressi dell'AND non possono essere contemporaneamente a livello H.

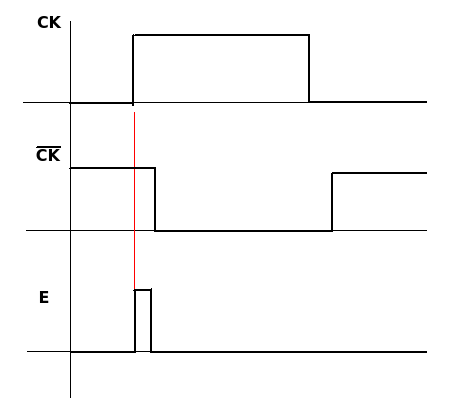

Tuttavia, a causa del ritardo di propagazione introdotto dal NOT, esiste in realtà un brevissimo intervallo di tempo durante il quale entrambi gli ingressi dell'AND sono effettivamente a livello H, come mostra la figura seguente:

Come si può notare il segnale di abilitazione E che giunge al latch D ha una durata brevissima, pari in pratica al ritardo di propagazione della porta NOT. Di conseguenza l'intervallo di memorizzazione del latch risulta brevissimo e può essere sincronizzato con grande precisione, come vedremo fra breve.

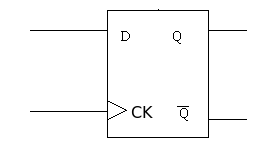

Flip flop D pilotato sul fronte di salita

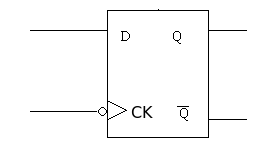

Il circuito precedente si chiama flip flop D pilotato sul fronte di salita (positive edge triggered D flip flop) e ha il seguente simbolo e tabella di verità:

|

|

L'ingresso CK è detto clock e il simbolo ↑ sta a indicare un fronte di salita del clock, cioè una commutazione del clock da livello basso L a livello alto H. La tabella di verità dice che il flip flop D memorizza il dato presente sull'ingresso D in corrispondenza del fronte di salita del segnale di clock.

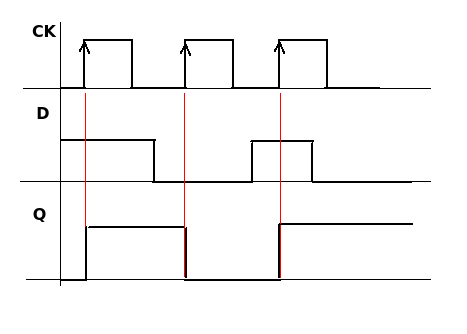

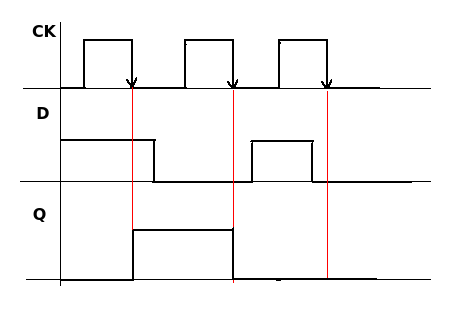

Si noti il simbolo del triangolino usato per l'ingresso CK. Tale simbolo sta a indicare che CK è un segnale attivo sul fronte (e non un segnale attivo sul livello, come per esempio D). Il seguente diagramma temporale dovrebbe chiarire meglio il funzionamento:

Si osservi che la commutazione dell'uscita Q risulta perfettamente sincronizzata con i fronti di salita del clock. Anche se D cambia valore quando CK è a livello H, tale valore non viene memorizzato (tranne che in corrispondenza del fronte).

A differenza del latch D, che risulta trasparente al dato di ingresso per tutta la durata del segnale di abilitazione, il flip flop D è sincronizzato col fronte del clock.

Il segnale di clock

Come avremo modo di vedere meglio nel seguito, il segnale di clock è estremamente importante all'interno di un circuito logico, in quanto consente di sincronizzare fra loro dispositivi logici diversi. Come nell'esempio appena visto, il segnale di clock è generalmente un segnale periodico che, come una sorta di metronomo, batte il tempo per orchestrare il funzionamento di tutti i circuiti collegati fra loro.

Assomiglia al segnale di abilitazione (enable) dal quale in un certo senso deriva, ma rispetto a questo consente una sincronizzazione precisa sui fronti (di salita o di discesa), mentre l'abilitazione è attiva per tutta la durata del segnale. Inoltre mentre in un circuito solitamente i segnali di abilitazione sono locali (cioè si riferiscono a pochi integrati collegati fra loro), il clock è un segnale globale, collegato a tutti i dispositivi che devono essere sincronizzati fra loro.

La frequenza del segnale di clock è molto importante per valutare le prestazioni di un sistema digitale (per esempio un calcolatore) in quanto da essa dipende la velocità del sistema stesso (frequenza maggiori corrispondono a velocità più elevate).

Flip flop D pilotato sul fronte di discesa

Sostituendo la porta AND con una porta NOR si può realizzare un flip flop D pilotato sul fronte di discesa del clock (negative edge triggered D flip flop), come il lettore può facilmente verificare per proprio conto:

Il simbolo e la tabella di verità sono i seguenti:

|

|

Si noti il simbolo di negazione (il "pallino") sull'ingresso CK che sta a indicare che il segnale è attivo sul fronte di discesa. Il seguente cronogramma chiarisce ulteriormente il funzionamento:

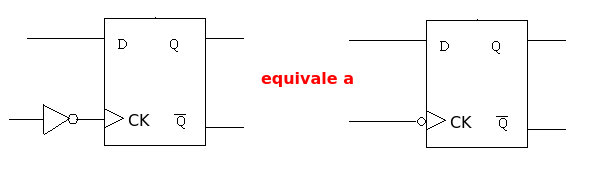

E' facile anche osservare che è possibile trasformare un ff pilotato sul fronte di salita del clock in uno pilotato sul fronte di discesa (o viceversa) semplicemente aggiungendo una porta NOT sull'ingresso di clock:

Tastierino numerico con flip flop D

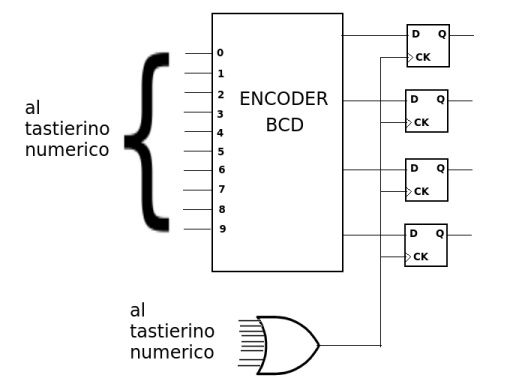

Consideriamo di nuovo il circuito di memorizzazione dei codici prodotti da un tastierino numerico, usando però stavolta una serie di flip flop D per la memorizzazione dei codici:

Si osservi che in questo modo i problemi di sincronizzazione sono stati risolti. Infatti la memorizzazione del dato nei flip flop avviene in corrispondenza del fronte di salita di CK, cioè quando un tasto viene premuto. Quando il tasto viene rilasciato invece (fronte di discesa) il dato è ormai memorizzato nei flip flop e non viene più modificato.

Sito realizzato in base al template offerto da

http://www.graphixmania.it