Un registro seriale (detto anche SISO = Serial Input Serial Output o Shift Register) è un registro in cui la scrittura e la lettura dei dati avvengono in modo seriale, cioè un bit alla volta.

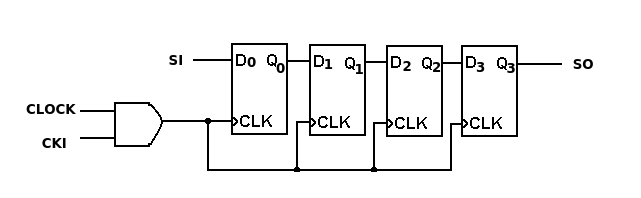

Si consideri la seguente struttura circuitale:

Si noti che i 4 ff sono collegati tutti in cascata, cioè con l'uscita di ognuno collegato con l'ingresso di quello successivo.

L'ingresso SI è detto Serilal Input, cioè ingresso seriale. Esso coincide con l'ingresso D0 del primo flip flop. Per scrivere il dato nel registro (4 bit) occorre abilitare il CLOCK con CKI = H (clock inibit) e quindi fornire i 4 bit uno alla volta sull'ingresso SI. I bit verranno memorizzati nei 4 ff ad ogni fronte di salita del clock. Si osservi che i bit scorrono (da cui il nome di registro a scorrimento o shift register) da sinistra a destra ad ogni fronte del clock.

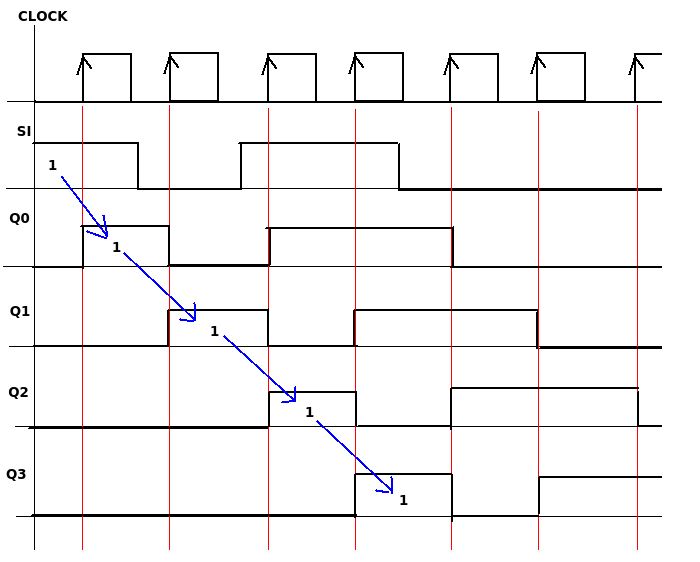

Dopo 4 fronti di salita il primo bit inserito sarà disponibile sull'uscita SO (serial output, coincidente con l'uscita Q3 dell'ultimo flip flip). Occorreranno quindi altre 3 fronti del clock perché tutti e 4 i bit memorizzati "escano" dal registro. La lettura, come si può notare, è in questo caso distruttiva. Il seguente diagramma temporale dovrebbe chiarire meglio il funzionamento del circuito:

Le frecce in blu indicano lo spostamento del primo bit del dato di ingresso da un flip flop a quello successivo.

Ritardo di propagazione e tempo di hold

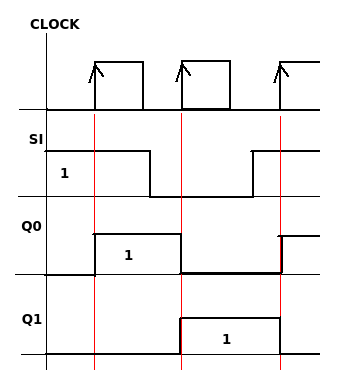

Si noti che, affinché il circuito funzioni correttamente, occorre che all'arrivo del fronte del clock il fliop flop successivo abbia il tempo di memorizzare il valore in uscita dal flip flop precedente prima che quest'ultimo cambi a sua volta. Osserviamo per esempio più nel dettaglio quello che accade all'arrivo del seconco fronte di clock alle uscite Q0 e Q1:

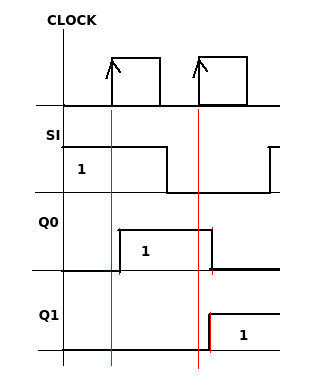

Sebbene nel nostro diagramma temporale tutte le commutazioni appaiano perfettamente sincronizzate con i fronti di clock, nei flip flop reali tuttavia sono presenti tempi di ritardo e in particolare:

- Ritardo di propagazione del flip flop

E' il tempo che passa dalla commutazione del segnale di ingresso alla corrispondente commutazione del segnale di uscita. - Tempo di hold del flip flop.

E' il tempo minimo in cui l'ingresso del flip flop deve rimanere stabile dopo il fronte del clock affinché la lettura del flip flop sia corretta.

Nei circuiti digitali reali i tempi di propagazione sono sempre maggiori dei tempi di hold, in modo da garantire che, all'arrivo del fronte del clock, la lettura dei dati avvenga correttamente. La figura seguente mostra un diagramma temporale "reale" in cui viene messo in evidenza l'effetto dei tempi di ritardo nel funzionamento del nostro registro:

Sito realizzato in base al template offerto da

http://www.graphixmania.it