Consideriamo ora un caso estremamente semplice. Supponiamo che il nostro microcomputer disponga di un'unica periferica e che tale periferica sia costituita da un'unica coppia di display a 7 segmenti (periferica di output).

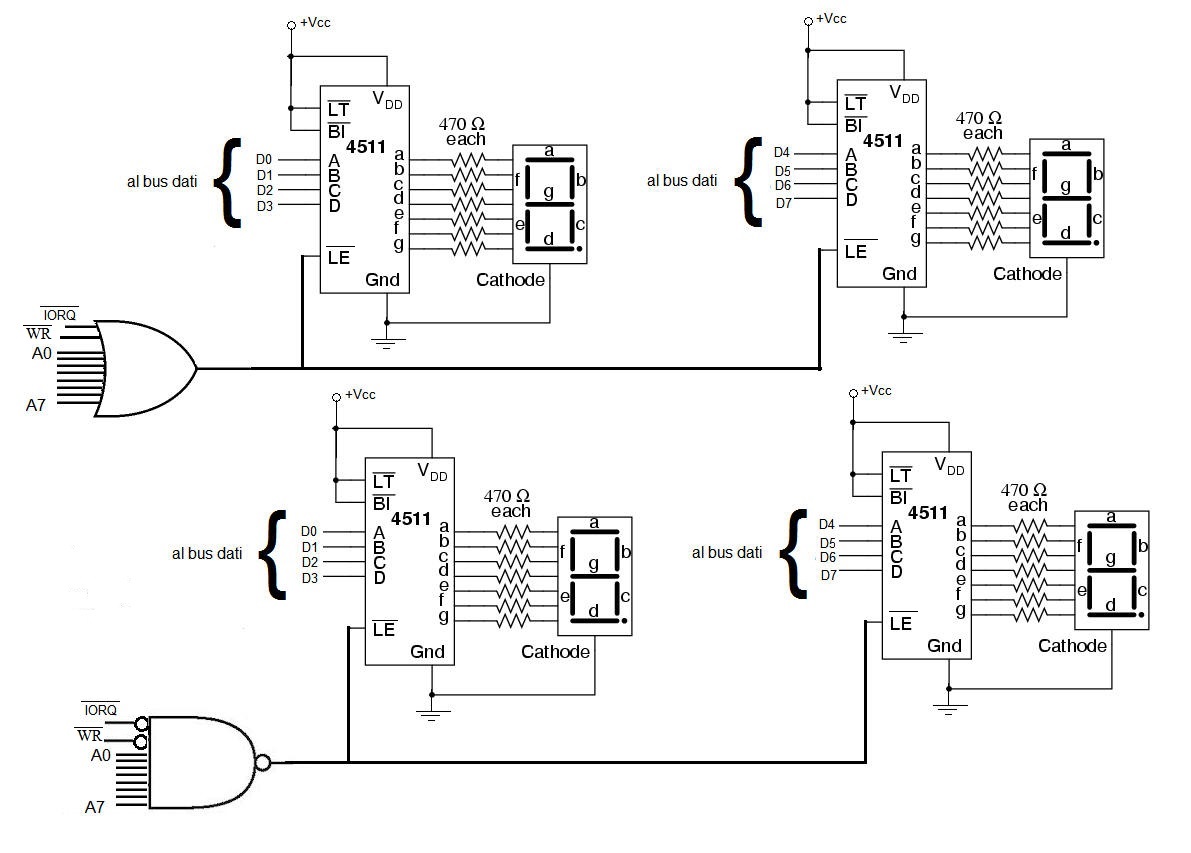

Siccome nel sistema non sono presenti altre periferiche di nessun tipo, il circuito di collegamento è estremamente semplice:

L'integrato 4511 è un latch/decoder/driver per display a 7 segmenti. In pratica è un dispositivo per pilotare un display a 7 segmenti che converte un valore BCD sugli ingressi ABCD nell'opportuna visualizzazione del numero corrispondente sul display. Inoltre il 4511 contiene anche al proprio interno 4 latch che consentono la memorizzazione del valore (se LE è basso, i latch leggono il dato; se LE è alto, i latch memorizzano e mantengono il dato acquisito).

Si noti che i due display sono collegati rispettivamente con i 4 bit inferiori e i 4 bit superiori del bus dati. Essendo la situazione così semplice, il bus indirizzi non viene utilizzato. Infatti, come si è detto, nel sistema è presente quest'unica periferica e dunque non c'è bisogno di usare gli indirizzi per distinguere una periferica da un'altra.

In pratica qualsiasi istruzione OUT su qualsiasi indirizzo provocherà l'abbassamento di IORQ e di WR e di conseguenza la memorizzazione del valore presente sul bus dati nei due integrati 4511. Tanto per fare un esempio, le seguenti istruzioni:

OUT (00h),A ; invia A all'indirizzo 00h

provocano la visualizzazione del numero 35 sui due display (3 sul display collegato con D4-D7 e 5 su quello collegato su D0-D3). L'indirizzo 00h usato nella OUT non ha nessuna importanza: qualsiasi indirizzo sarebbe andato ugualmente bene, dal momento che la periferica non utilizza il bus indirizzi.

Consideriamo ora il caso leggermente più complesso in cui si desideri pilotare 4 display a 7 segmenti. In questo caso abbiamo bisogno di usare due porte di uscita per specificare quale delle due coppie di display si vogliono indirizzare. Di conseguenza occorre usare il bus indirizzi.

Supponiamo arbitrariamente di assegnare l'indirizzo 00h alla prima coppia di display e FFh (tutti i bit a 1) alla seconda coppia. Il circuito di pilotaggio è il seguente:

Si osservi il ruolo della porta OR e della porta NAND. L'OR fornisce in uscita un livello L solo quando tutti i suoi ingressi sono L, cioè quando è selezionato l'indirizzo 00h e quando IORQ = L e WR = L. Invece la porta NAND fornisce L solo quando tutti gli ingressi sono H, cioè quando viene selezionato l'indirizzo FFh e quando IORQ = L e WR = L.

Le porte OR e NAND in questo esempio eseguono una semplice decodifica dell'indirizzo. Supponendo di voler scrivere il valore 3 su tutti e 4 i display la sequenza di istruzioni necessaria è la seguente:

OUT (00h),A ; invia A all'indirizzo 00h

OUT (0FFh),A ; invia A all'indirizzo FFh

In questo caso i due indirizzi sono indispensabili e non sono scelti a caso: essi corrispondono agli indirizzi delle due porte di uscita associate alle due coppie di display.

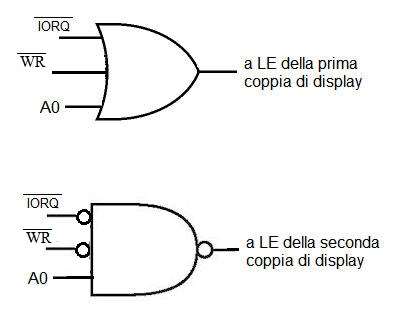

In realtà nel caso precedente, se il sistema ha solo due porte di output, è possibile una soluzione circuitalmente possibile, che fa uso della cosiddetta decodifica parziale degli indirizzi. Nella figura seguente per semplicità sono state indicate solo le due porte OR e NAND:

Si noti che in questa soluzione è stato usato solo bit zero (A0) del bus indirizzi per distinguere fra loro gli indirizzi delle due porte (00h e FFh). Questo tipo di decodifica è detta anche ambigua poiché esistono più indirizzi associati alla stessa porta (nel nostro caso tutti gli indirizzi che terminano con 0, ovvero gli indirizzi pari, sono associati alla prima coppia di display, mentre tutti gli indirizzi dispari sono associati alla seconda coppia). Tuttavia se nel sistema sono presenti solo due porte (come nel nostro esempio) la decodifica ambigua non costituisce un problema, poiché in realtà abbiamo bisogno di distinguere solo due indirizzi diversi.

Sito realizzato in base al

template offerto da

http://www.graphixmania.it