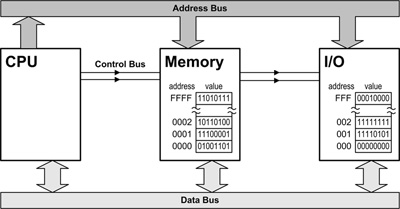

Nell'architettura di von Neumann solo la CPU può scrivere sul bus indirizzi. mentre gli altri dispositivi funzionano solo in lettura. Invece sul bus dati tutti possono leggere e scrivere e questo può potenzialmente provocare conflitti sul bus.

Alcuni dispositivi sono attivi e possono iniziare il trasferimento (lettura o scrittura) dei dati, altri invece sono passivi e aspettano la richiesta di trasferimento. I dispositivi attivi sono chiamati master, i passivi invece slave. Per esempio quando la CPU ordina al controllore del disco di leggere o scrivere un blocco, la CPU si comporta come master mentre il controllore come slave. Alcuni dispositivi si comportano da master oppure da slave, a seconda delle operazioni effettuate. La tabella seguente mostra alcuni esempi di master e slave in alcune tipiche operazioni compiute in un calcolatore:

Per il corretto funzionamento un solo dispositivo fra quelli collegati allo stesso bus può agire in un dato momento come master. Se esistono due o più master è necessario un arbitro del bus, cioè un dispositivo che stabilisca chi in quel momento può comportarsi da master, cioè iniziare un trasferimento dati sul bus.

Nella situazione più semplice, possiamo supporre che l'unico master sia la CPU e che tutti gli altri dispositivi si comportino da slave. Dunque è la CPU a stabilire in ogni istante quali dispositivi possono scrivere oppure leggere dal bus. La CPU, master del sistema, gestisce lo scambio di informazioni.

Tutti i dispositivi (tranne la CPU stessa) presenti nel microcalcolatore possiedono un particolare e univoco spazio di indirizzi, rappresentato da un intervallo numerico che identifica il dispositivo. Supponiamo per esempio che la CPU necessiti di trasmettere un dato al dispositivo di uscita di indirizzo <n>. La CPU invia l’indirizzo <n> all’intero sistema, tramite il Bus degli Indirizzi. Tutti i dispositivi sono all’ascolto, ma soltanto uno riconoscerà il proprio indirizzo, e solo questo dispositivo attiverà i suoi circuiti in modo da mettersi in grado di ricevere il dato.

A questo punto, la CPU trasmetterà il dato sul Bus dei Dati, che sarà acquisito soltanto dal dispositivo attivo. Tutto questo avviene, naturalmente, con il supporto di opportuni segnali aggiuntivi di controllo e di temporizzazione (vedi oltre, Bus di controllo).

All’opposto, supponiamo ora che la CPU voglia ricevere un dato da un dispositivo di ingresso di indirizzo <m>. Anche in questo caso la CPU invia l’indirizzo <m> all’intero sistema, tramite il Bus degli Indirizzi. Soltanto un dispositivo riconoscerà l’ indirizzo <m>, e solo questo dispositivo attiverà i suoi circuiti in modo da mettersi in grado di inviare il dato. Ottenuto questo, la CPU si mette in attesa del dato, che il dispositivo attivo invierà tramite il Bus dei Dati.

Bus di controllo

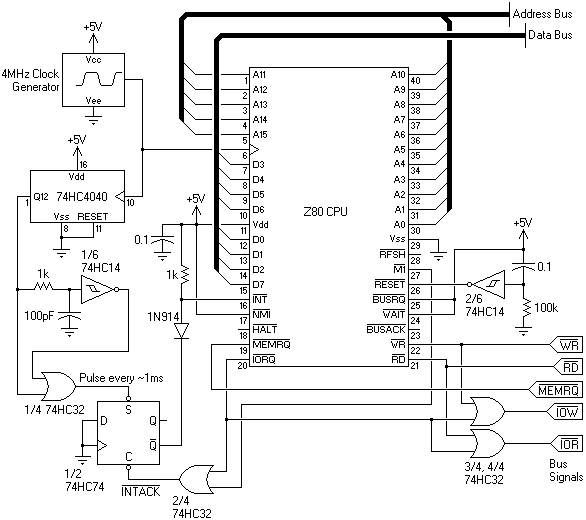

Spesso nell'architettura di un calcolatore alcune linee vengono indicate come bus di controllo (control bus). Forse il nome è un po' fuorviante, in quanto il bus di controllo, a differenza del bus dati e indirizzi, non è costituito da un insieme di linee omogenee per scopo. Esso è formato da tutti quei segnali di controllo che la CPU deve inviare agli altri dispositivi per coordinarne il funzionamento (per esempio fanno parte del bus di controllo i segnali di READ e WRITE in memoria).

A titolo di esempio si dia un'occhiata al seguente schema che utilizza il microprocessore Z80. Il bus di controllo è costituito da tutti quei segnali "sparsi" che non fanno parte del bus indirizzi e del bus dati:

Sito realizzato in base al template offerto da

http://www.graphixmania.it